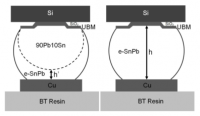

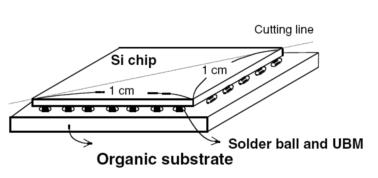

Wie das amerikanisches UCLA Institut für angewandte Werkstoffwissenschaften in einem unlängst veröffentlichten Bericht erläutert, erhöht sich die Wahrscheinlichkeit eines Kontaktdefektes bei Verbundlötstellen im Halbleiterbereich erheblich. Eben jene kamen bei Nvidias Grafikchips bis vor Kurzem zum Einsatz und sollen der Grund für die aktuellen Probleme bei diesen sein.

Durch die verschiedenen Festigkeiten und Elastizitäten der stark bleihaltigem Kontaktstellen an der Unterseite des Siliziumchips und des eutektischen Lötmittels kommt es zu Spannungen, die in der Theorie ein bis zu hundertfach erhöhtes Ausfallrisiko mit sich bringen. In der Praxis soll immerhin noch ein zehnfach so hohes Risiko gegenüber der Kombination aus rein eutektischen Kontaktstellen und Lötmittel bestehen.

AMD setzt bei seinen ATI Radeon-Grafikchips auf diese Kombination und muss bislang keine erhöhtes Defektaufkommen beklagen.

Quelle: UCLA

Neueste Kommentare

26. März 2026

25. März 2026

25. März 2026

25. März 2026

24. März 2026

8. März 2026