Bis zum voraussichtlichen Start der neuen Generation von CPUs des Herstellers AMD sind es nur noch wenige Monate. Die Entwicklung ist so gut wie abgeschlossen, doch nun mehren sich laut PCWatch die Klagen der Chipsatzentwickler. Durch die beim Hammer in die CPU verlagerte Schnittstelle zum Hauptspeicher entstehen Probleme, wenn Mainboards mit im Chipsatz integrierter Grafik entwickelt werden sollen.

AMD will auf längere Sicht die gesamte Prozessorfamilie auf dem Hammer Kern aufbauen. Die Segmente Mainstream, Performance Desktop und mobile CPUs will man noch im Jahr 2003 mit Varianten des Hammers besetzten. AMD’s CPU für den low-cost Markt soll erst 2004 auf der Hammer Technologie basieren. Dies ist kein Problem, da auch nach der Einführung des ersten SlotA Athlons über ein Jahr verging, bis der Duron im low-cost Segment die Position des K6 als Einstiegsprozessor ersetzte.

Durch die in der Hammer Architektur in die CPU verlagerte Schnittstelle des Hauptspeichers ergeben sich Probleme, wenn Chipsätze mit UMA-Grafik entwickelt werden sollen. „UMA“ bedeutet „unified memory architecture“ und ist die Verwendung noch eines zentralen RAM-Systems. Dieses soll primär die einzelnen Speichersysteme in Grafikkarte und Hauptspeicher zu einem einzigen zusammenfassen. Heute wird dieses System hauptsächlich dazu verwendet, um kostensenkend die Funktionalität der Grafikkarte in den Chipsatz zu verlagern. Damit kann der teure schnelle Speicher auf der Grafikkarte ebenfalls eingespart werden, da mit der UMA-Architektur der Hauptspeicher für diese Aufgabe herhält.

Das Problem von UMA-Grafik mit der Hammer Architektur liegt nun daran, dass für jedes von der Grafikkarte an den Monitor ausgegebene Bild der Framebuffer komplett ausgelesen werden muss. Bei einer angenommenen Bildwiederholfrequenz von 85Hz muss dies demzufolge auch garantiert 85 mal pro Sekunde ohne jede Verzögerung erfolgen können. Wenn es dabei zu Verzögerungen kommt, gerät der RAMDAC aus dem Tritt und eine saubere Grafikausgabe wird unmöglich. Bei klassischen Architekturen ist dies kein Problem, da die Verwaltung des Hauptspeichers hier dem Chipsatz obliegt. Dieser kann demzufolge festlegen, ob zu einem bestimmten Zeitpunkt der Grafikkern beim Speicherzugriff Priorität hat oder andere Komponenten wie CPU oder PCI-Master. Wenn die Kontrolle aber vollständig in der CPU liegt, muss diese auf diese Anforderung vorbereitet sein. Scheinbar ist dies mit der derzeitigen Version des K8 („Hammer“) noch nicht geschehen. Desweiteren könnten auch Stromsparmechanismen mobiler Hammer-Varianten zum Problem für UMA werden, wenn diese die Taktfrequenz des Prozessors herabsetzen. Verstärkt wird das Problem auch durch die mittlerweile sehr populären „dual display“ Grafikchips. Dadurch verdoppelt sich die Anforderung an den Framebuffer nochmals.

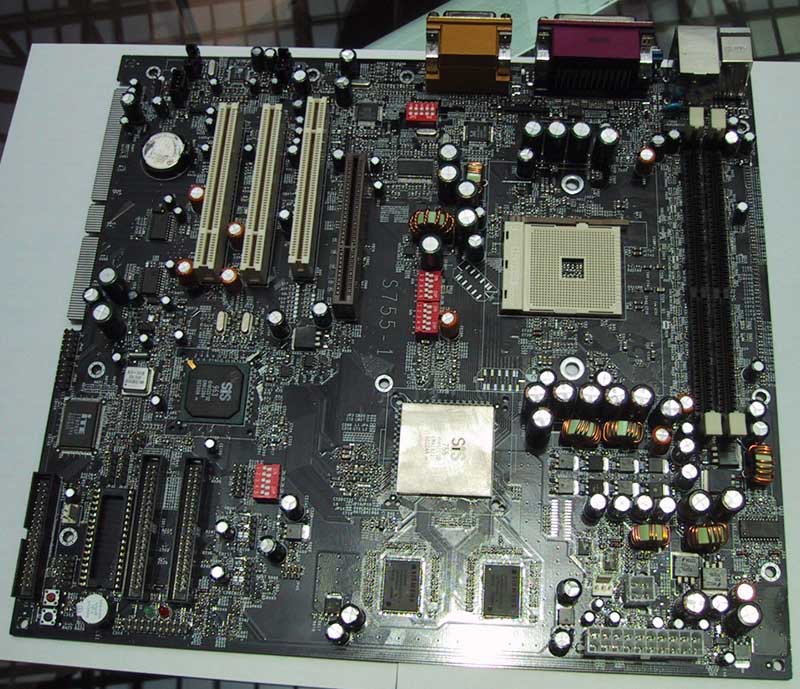

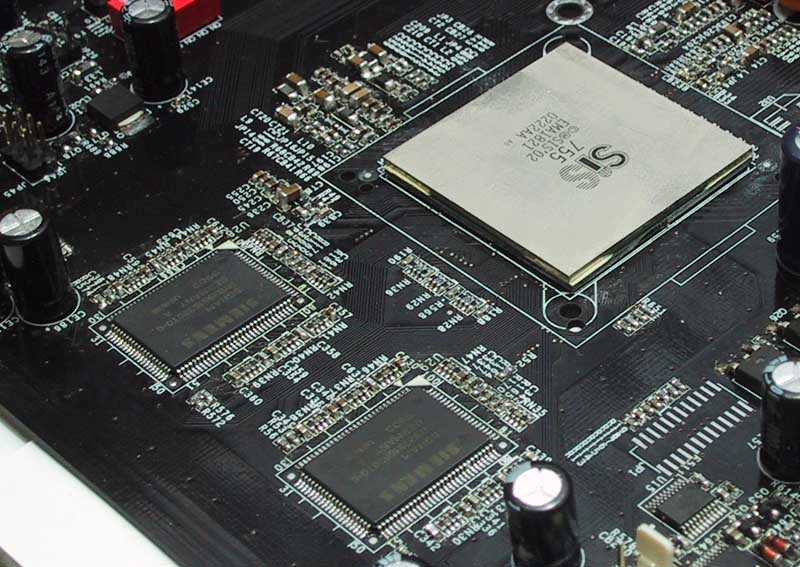

Um dem abzuhelfen, soll die Speicherschnittstelle der 2. Generation des Hammer Kerns auch für UMA-Grafik vorbereitet sein. Da UMA-Grafik hauptsächlich im low-cost Segment eingesetzt wird, und der Duron erst 2004 auf dem Hammer aufsetzen soll, wird dies nicht zu einem Problem für AMD werden. Als Übergangslösung für auf dem Mainboard integrierte Grafik könnten sich bis dahin Chipsätze mit separatem Framebuffer etablieren. Das Engineering Sample eines SiS755-Mainboards ist scheinbar schon mit dieser Lösung ausgestattet, gut sichtbar auf den Bildern unter dieser News.

Quelle: PCWatch

Neueste Kommentare

8. Mai 2026

5. Mai 2026

3. Mai 2026

3. Mai 2026

29. April 2026

28. April 2026