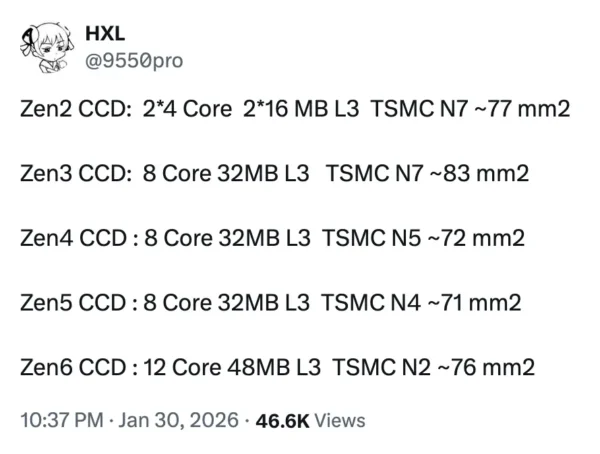

Rund um AMDs kommende „Zen 6“ Mikroarchitektur verdichten sich die Hinweise auf einen tiefgreifenden Umbau auf Chiplet-Ebene. Im Fokus steht dabei der sogenannte „CPU Core Complex Die“ (CCD) – das zentrale Bauelement der Ryzen- und EPYC-Prozessoren. Aktuelle Gerüchte deuten darauf hin, dass AMD hier erstmals einen deutlichen Schritt nach vorne machen könnte: Statt wie bisher 8 Kerne soll ein Zen-6-CCD künftig bis zu 12 CPU-Kerne integrieren. Das entspräche einem Plus von 50 Prozent pro Chiplet und wäre eine Premiere für AMDs leistungsstarke und voll ausgebaute CCDs im Desktop- und Server-Bereich.

Bislang setzte AMD höhere Kerndichten meist über alternative Ansätze um, etwa kompaktere Kerne oder Designs, die nicht primär auf maximale Taktraten ausgelegt waren. Zen 6 könnte diese Trennung aufheben. Parallel zum Kernzuwachs ist auch von einem deutlich größeren gemeinsamen Level-3-Cache die Rede. Demnach sollen alle 12 Kerne in einem einzigen CCX zusammengefasst sein und auf einen gemeinsamen, 48 MByte großen L3-Cache zugreifen. Zum Vergleich: Aktuelle 8-Core-CCDs bieten 32 MByte L3. Auch hier ergibt sich also eine Skalierung um 50 Prozent.

Ein einzelner CCX mit allen Kernen hätte zudem strukturelle Vorteile. Interne Kommunikation und Cache-Zugriffe könnten vereinheitlicht werden, was insbesondere bei Latenz-sensitiven Anwendungen interessant ist. Wie stark sich das in der Praxis auswirkt, hängt jedoch weiterhin von Faktoren wie Infinity Fabric, Speicherlatenzen und dem Scheduling des Betriebssystems ab.

Ähnliches wurde bereits im Juli 2025 berichtet. Schon damals gab es ein Gerücht, dass AMDs Zen-6-CPUs mit mehr Kernen pro CCD kommen könnten. Deshalb wurde Zen 6 als Weiterentwicklung bei Kernen und Speicherbandbreite bezeichnet. Das erneute Gerücht schlägt in die selbe Kerbe.

Technisch plausibel wird dieser Schritt vor allem durch den erwarteten Fertigungswechsel. Zen-6-CCDs sollen Gerüchten zufolge bei TSMC im N2-Prozess gefertigt werden, einer 2-Nanometer-Klasse mit Nanosheet-Transistoren. Im Vergleich zum für Zen 5 genutzten N4P-Knoten (4 nm, FinFET) bietet N2 eine deutlich höhere Transistordichte. Entsprechend heißt es, dass der Zen-6-CCD trotz mehr Kernen und größerem Cache nur leicht wachsen soll: von rund 71 mm² bei Zen 5 auf etwa 76 mm² bei Zen 6. Das würde AMD erlauben, Kosten, Ausbeute und Chiplet-Strategie in vertrauten Bahnen zu halten.

Besonders spannend für Enthusiasten ist der Ausblick auf X3D-Modelle. Zen 6 soll weiterhin voll kompatibel mit 3D V-Cache sein. In diesem Kontext kursieren Zahlen von bis zu 144 MByte L3-Cache pro CCD. Bei einem Desktop-Prozessor mit zwei CCDs auf dem AM5-Sockel wären theoretisch bis zu 288 MByte L3 möglich – ein enormer Wert, insbesondere für Gaming und andere Cache-lastige Workloads. Interessant ist das auch im Wettbewerbsumfeld, da Intels kommende „Nova Lake-S“ CPU-Generation ebenfalls verstärkt auf größere Last-Level-Caches setzen soll.

Wie immer gilt: Vor einer offiziellen Ankündigung sind diese Angaben mit Vorsicht zu genießen. Doch selbst als grobe Richtung betrachtet, deutet vieles darauf hin, dass Zen 6 kein bloßes Feintuning wird, sondern einen strukturellen Sprung auf Chiplet-Ebene markieren könnte.

Quelle: HXL @ X

Neueste Kommentare

8. März 2026

6. März 2026

4. März 2026

3. März 2026

2. März 2026

2. März 2026