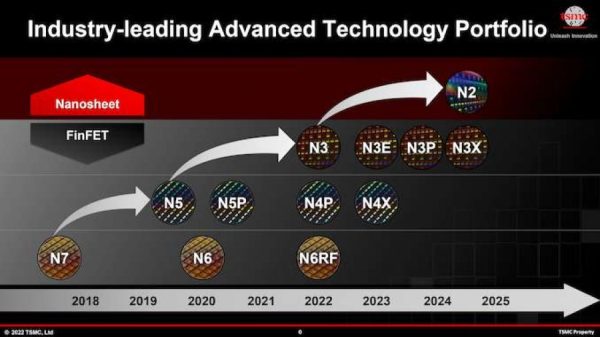

Der taiwanesische Auftragsfertiger TSMC hat sich dazu geäußert, wie es mit neuen Fertigungsverfahren vorangeht. So erklärte man im Rahmen des TSMC Technology Symposium 2022, dass in der zweiten Jahreshälfte die Fertigung im 3-Nanometer-Verfahren aufgenommen werde. 2025 will man dann so weit sein und in 2 nm herstellen.

Dabei teilt sich das 3-Nanometer-Verfahren in fünf Stufen auf, die jeweils mehr Möglichkeiten eröffnen, da sie eine höhere Transistoren-Dichte und mehr Effizienz erlauben. Konkret staffelt sich die 3-Nanometer-Herstellung bei TSMC folgendermaßen:

- N3

- N3E (Enhanced)

- N3P (Performance Enhanced)

- N3S (Density Enhanced)

- N3X (Ultra High Performance).

Das 2-Nanometer-Verfahren soll dann bei gleichbleibendem Strombedarf die Leistung um 10 bis 15 % erhöhen bzw. im Vergleich mit dem N3E-Verfahren den Strombedarf um 25 bis 30 % senken. Ein wichtiger Schritt sind dabei auch die GAAFETs Gate-All-Rround-Field-Effect-Transistors).

Als Vergleich: Samsung fertigt ebenfalls noch 2022 in 3 Nanometern und will ab 2025 wie TSMC dann auf die 2-Nanometer-Fertigung setzen. Allerdings sind die Verfahren der beiden Auftragsfertiger höchst unterschiedlich, sodass im Grunde keine 1:1-Vergleiche mehr möglich sind.

Quelle: TSMC

Neueste Kommentare

26. März 2026

25. März 2026

25. März 2026

25. März 2026

24. März 2026

8. März 2026