Im Rahmen seiner „Next Horizon“ Veranstaltung hat AMD nicht nur die neuen Radeon Instinct MI50 und MI60 Compute-Beschleuniger auf Basis von ‚Vega‘ 7-nm-GPUs vorgestellt, sondern auch seine neue EPYC ‚Rome‘ Server-CPU auf Basis von „Zen 2“ demonstriert und einige weitere Details zur Architektur verraten.

Zen 2 wird eingeführt eben mit dem neuen EPYC Server-Prozessor aus der 7-Nanometer-Fertigung (Codename ‚Rome‘) und nach Angaben von AMDs „Chief Technology Officer“ (CTO) Mark Papermaster ermöglicht der neue 7-nm-Prozess von TSMC eine doppelt so hohe Transistordichte auf gleichem Raum wie die 14-nm-FinFET-Technik von GlobalFoundries, die AMD bislang genutzt hatte. Die neue 7-nm-Produktion erlaube die gleiche CPU-Performance wie bisher bei halbem Strombedarf oder 25 Prozent mehr Leistung bei gleicher Stromaufnahme.

Die durch die neue Fertigung ermöglichten Transistoren erlauben Verbesserungen zur bisherigen ‚Zen‘ Architektur in einigeen wichtigen Punkten. Zen 2 habe im Vergleich zum Vorgänger eine deutlich verbesserte Sprungvorhersage bekommen, einen intelligenteren Befehls-Prefetch, einen optimierten Befehls-Cache und einen größeren Cache für die sogenannten Micro-Operationen von bereits decodierten Befehlen. Außedem wurden die SIMD-Befehlsregister von 128 auf 256 bit vergrößert, was die Architektur damit auf das gleiche Niveu hievt wie die Intel ‚Skylake‘ Mikroarchitektur, die bei der Einzelkern-Leistung immer noch deutlich vor den bisherigen AMD Ryzen liegt.

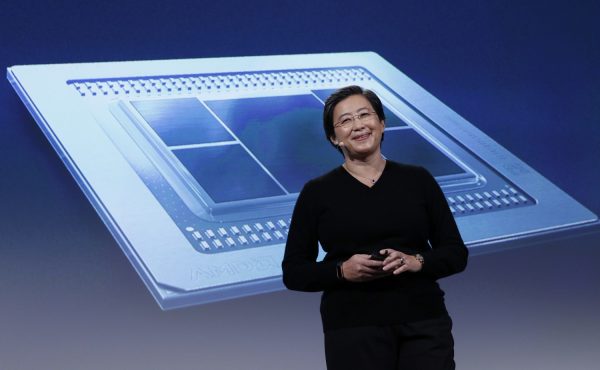

- AMD Lisa Su Next Horizon

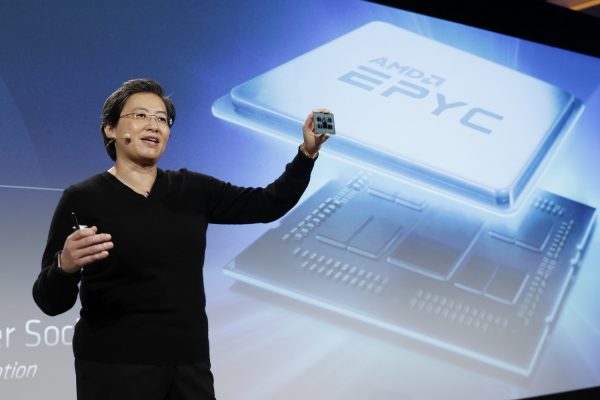

- AMD Lisa Su und EPYC

- AMD Mark Papermaster erklärt Zen 2

Die neue AMD EPYC Server-CPU ist also der Vorreiter der neuen Architektur und kommt im Laufe des nächsten Jahres mit 64 „Zen 2“ Kernen plus

- Worlds First 7nm Datacenter CPU

- 7nm drives Compute Efficiency

- Industry-First PCIe 4.0

- New Front End Advances

- Floating Point Advances

- High-Performance Momentum

Quelle: Pressemitteilung

Neueste Kommentare

24. März 2026

8. März 2026

6. März 2026

4. März 2026

28. Februar 2026

26. Februar 2026