Interner Ring-Bus & L3-Cache

Die CPU-Kerne von Sandy Bridge haben wir nun recht ausführlich behandelt und gehen zu einem der wichtigsten Merkmale der Sandy Bridge Architektur über.

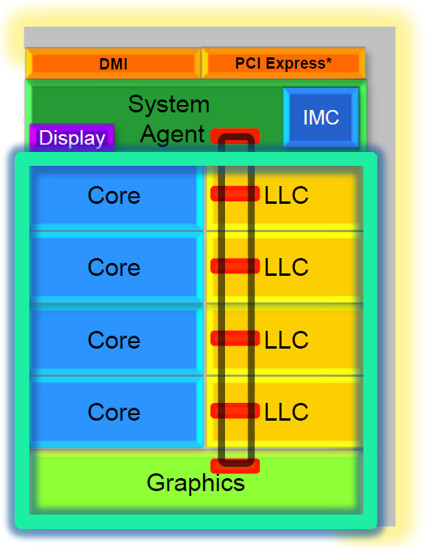

Ring-Struktur im Sandy Bridge Prozessor (Quelle: Intel)

Der Ring-Bus verbindet alle Komponenten des DIEs, also die Grafik, die CPU-Kerne, den L3-Cache und den System Agent. Es gibt eigentlich vier Ringe: ein 32 Byte breiter Datenring sowie ein Request-, ein Acknowledge- und ein Snoop-Ring, welche für die korrekte Funktionsweise zuständig sind. Auch wenn es ein Ring-Bus ist, so ist es nicht notwendig, dass die Daten den kompletten Ring durchlaufen, sondern es wird automatisch der kürzeste Pfad gewählt. Dafür hat jeder CPU-Kern zwei Agents, die in der Grafik jeweils nach oben oder unten senden können, je nach Zieladresse.

Der Bus arbeitet mit der gleichen Spannung und Frequenz wie die CPU-Kerne. Laut Intel ist der Bus so leistungsfähig, dass er auch für zukünftige CPUs mit mehr als vier Kernen nicht verändert werden müsse.

Der Cache selbst ist je nach CPU unterschiedlich groß. Generell gibt es mehrere so genannte Cache-Boxen. Physikalisch sind diese getrennt, wodurch eine höhere Bandbreite erreicht wird. Die CPU-Kerne sehen aber nur einen logisch zusammenhängenden Cache. Dieser Cache steht nicht nur den CPU-Kernen zur Verfügung, sondern wird auch von der (integrierten) Grafik genutzt.

Neueste Kommentare

12. Mai 2026

12. Mai 2026

12. Mai 2026

12. Mai 2026

12. Mai 2026

10. Mai 2026