Auf dem Microprocessor Forum gab VIA Informationen zur Neuauflage des derzeit aktuellen C3-Prozessorkernes Nehemiah sowie dessen Nachfolger bekannt.

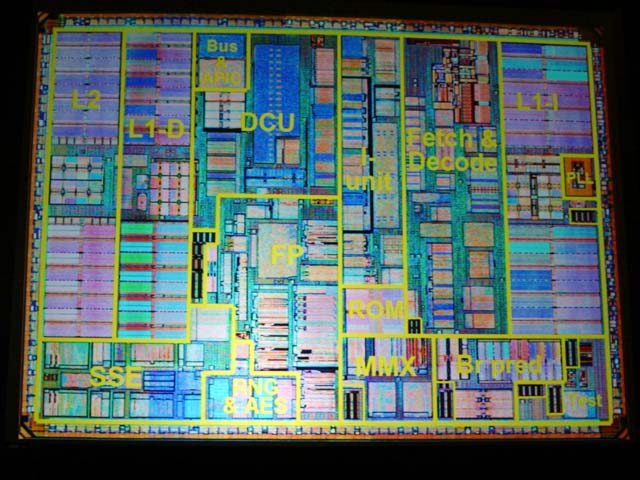

Der um 5% geschrumpfte Prozessorkern mit lediglich 20,4 Mio Transistoren wird über einen 200 MHz schnellen Frontsidebus mit dem Chipsatz verbunden. Die fünfzigprozentige Beschleunigung des FSB macht neue Chipsätze nötig. VIA liefert dazu den CM400. Erstmals unterstützt wird die Konfiguration von Zweiprozessorsystemen. Dazu werden zwei Prozessoren mit einem Frontsidebus (FSB) an den Chipsatz gekoppelt. Dank des neuen nanoBGA-Packages passen die zwei Prozessoren auf die gleiche Fläche wie bisher ein einziger Prozessor. Auf dem Microprocessor Forum konnte VIA bereits ein Mini-ITX-Mainboard mit zwei fest verlöteten Prozessoren zeigen.

Im nächsten Jahr wird der C5I alias Esther die Nachfolge des Nehemiah antreten. Der C5I wird im 0.09µm Prozess mit Silicon on Insulator Technologie (SOI) bei IBM gefertigt. SOI verringert die Leistungsaufnahme und ermöglicht höhere Performance.

Angestrebt wird eine Taktfrequenz von 2000 MHz. Dabei soll der Prozessor bei gleiche Performance nur noch die Hälfte der Leistungsaufnahme des Nehemiah erreichen.

Neben SOI werden noch SSE2 und eine verbesserte Sprungvorhersage die Leistung erhöhen.

Der mit 30mm² geradezu winzige Prozessor soll erstmals das Pentium 4 Busprotokoll unterstützen. Damit wäre VIA nicht mehr auf die bei Kunden nicht gerade beliebten eigenen Chipsätze angewiesen. Der Esther wäre kompatibel zu jedem Pentium 4 bzw. Pentium M Chipsatz und könnte gleichzeitig von der weit höheren Bandbreite des FSB profitieren.

Neben dem Pentium 4 Busprotokoll soll auch der sogenannte „VIA Bus“ unterstützt werden. Ob es sich dabei um eine Eigenentwicklung oder das bisher verwendete Pentium Busprotokoll handelt, wird sich noch herausstellen.

Erste Muster des Esther sollen im Dezember vom Band laufen.

Quelle: PC Watch

Neueste Kommentare

6. Mai 2026

6. Mai 2026

5. Mai 2026

3. Mai 2026

3. Mai 2026

29. April 2026