Der CPU-Kern – Speicherzugriff

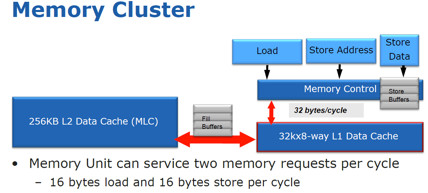

Was nützt einem eine schnelle Datenverabeitung, wenn die Datenbusse nicht hinterher kommen? Das war eine weitere Baustelle von Intel, welche bildlich sehr ähnlich wie AVX realisiert wurde. Bisher konnten pro Taktzyklus 16 Bytes geladen und gleichzeitig 16 Bytes geschrieben werden.

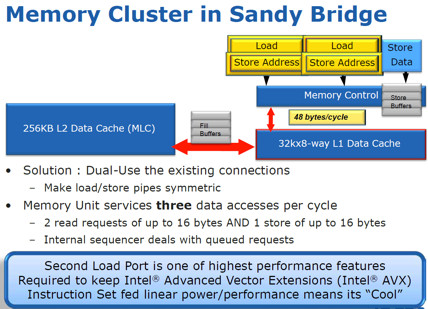

Dazu werden die bisherigen „Load“ und „Store Address“ Einheiten erweitert. Diese sind über jeweils einen Kanal (Pipe – nicht mit Dual-Channel zu verwechseln) zum Memorycontroller angebunden, welcher nun symmetrisch gestaltet wird. Damit werden zwar nicht die gleichzeitigen Schreib- und Lesezugriffe erhöht, da weiterhin nur zwei Kanäle bereit stehen, aber es können jetzt auch zwei gleichzeitige Lesezugriffe stattfinden. Wenn keine Speicheradresse geschrieben wird. Grafisch ist dies sicherlich einfacher zu verstehen.

Somit können nun gleichzeitig pro Takt bis zu 32 Bytes gelesen und 16 Bytes geschrieben werden.

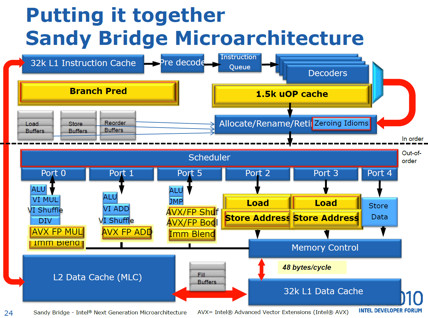

Alle Änderungen zusammengefasst sehen dann schon recht umfangreich aus.

Neueste Kommentare

24. März 2026

24. März 2026

8. März 2026

6. März 2026

4. März 2026

3. März 2026