Der CPU-Kern – Befehlsdekoder #2

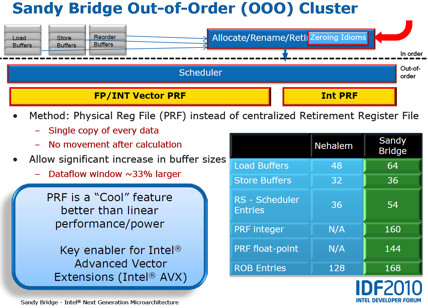

Doch die Out-Of-Order Architektur benötigt auch noch nach dem Rechenwerk einigen Aufwand, da die Ergebnisse wieder in die richtige Reihenfolge gebracht werden müssen. Außerdem ist es bei Out-Of-Order notwendig, mehrere Register (Speicherplätze für einzelne Werte) in der CPU bereit zu halten. Diese Register werden normalerweise unterteilt, so dass es verschiedene Typen für Quelldaten und Ergebnisse gibt. Da man dadurch die Daten mehrfach kopieren muss, hat Intel dies nun vereinheitlicht, wodurch unnötige Kopiervorgänge vermieden werden. Statt des sogenannten „Retirement Register File“ wurde die „Physical Register File“ eingeführt. Gleichzeitig wurde die Anzahl der Register und Puffer deutlich erhöht.

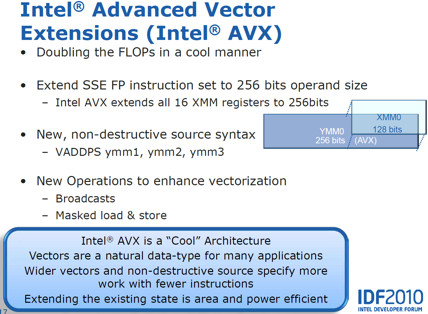

Dies ermöglicht auch die neue „Advanced Vector Extension“ von Intel, welche eine Erweiterung von SSE darstellt. Nun können 256 bit breite statt wie bisher maximal 128 bit breite Operanden genutzt werden. Werden wie bisher nur 128 bit genutzt, wird der Operand mit Nullen aufgefüllt. Außerdem werden neue Befehle eingeführt, die nun gleichzeitig drei bis vier Operanden beinhalten.

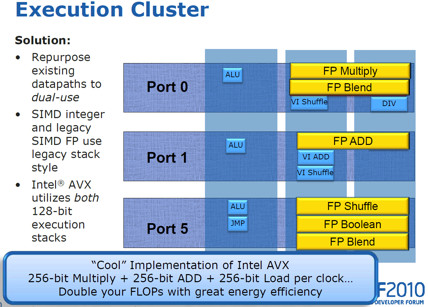

Um dies möglichst energieeffizient zu gestalten, sollten nicht haufenweise neue Schaltkreise benötigt werden. Daher gibt es nicht einfach zusätzliche Ausführungseinheiten, sondern die schon vorhandenen „Execution Units“ werden umgearbeitet. Bisher sah die Struktur folgendermaßen aus.

Es gibt drei sogenannte „Ports“, die jeweils drei „Stacks“ besitzen, welche für die Aufgaben GPR (Integer-Werte), SIMD INT (Single Instruction Multiple Data von Integer-Werten) oder SIMD FB (Single Instruction Multiple Data von Floating Point) zuständig sind. SIMD bedeutet, dass ein Befehl (z.B. Addition oder Multiplikation) auf viele verschiedene Daten angewandt wird, was dann meist parallel geschehen kann. Die findet man oft bei Multimedia Anwendungen.

Der Trick von Intel besteht vereinfacht gesagt darin, dass zwei Stacks zusammengefasst werden und so aus zwei 128 bit breiten Stacks ein quasi 256 bit breiter Stack.

Neueste Kommentare

8. März 2026

6. März 2026

4. März 2026

3. März 2026

2. März 2026

2. März 2026