Letzte Woche hat Samsung ein erstes, vorläufiges Datenblatt zu einem 512Mbit Speicherchip nach DDR-II Standard veröffentlicht. DDR-II soll der Nachfolger der derzeit in Serie produzierten DDR-SDRAMs werden. Nach dem Willen des JEDEC, dem Entwicklerforum um Speicherprodukte der Industrie, soll PC2700 der schnellste Vertreter von DDR-SDRAM nach DDR-I bleiben. Samsung und andere Hersteller wollen zwar noch Speichermodule mit 200MHz Taktfrequenz (DDR400/PC3200) im DDR-I Design bauen, dies wird jedoch nur von einem Teil der Industrie unterstützt. Das derzeitige Design stabil mit so hohen Taktfrequenzen zu betreiben ist schwierig und damit wenig wirtschaftlich in der Herstellung.

Aus Dokumenten der JEDEC und dem besagten Datenblatt kann man bereits einige sich abzeichnende Schlüsselfeatures der überarbeiteten Speicherform erkennen. Dies sind im Einzelnen:

- Neue FBGA (Fine pitch Ball Grid Array) Verpackung der Speicherchips. Diese im Speicherbereich noch recht junge Verpackungstechnik sorgt für geringere Abmessungen der verpackten Chips. Ausserdem besitzt sie gegenüber der klassischen TSOP-Verpackung einen geringeren induktiven Widerstand und bessere thermische Eigenschaften. Diese Art der Chipverpackung wird bereits beim Speicher aktueller Grafikkarten wie der Geforce 4 Ti Reihe verwendet.

- Absenkung der Versorgungsspannung der Speichermodule von derzeit 2,5V auf 1,8V. Dies trägt zu einer verringerten Stromaufnahme und damit besseren thermischen Eigenschaften bei.

- Eine verbesserte Zugriffsstrategie: „posted CAS“. Diese soll die Effizienz bei Kommandoübertragungen steigern.

- Die Latenz bei Schreibzugriffen liegt um einen Takt niedriger als bei Lesezugriffen. Dies steigert die Effizienz der Datenübertragung.

- Die Latenz bei Spaltenzugriffen auf die Speichermatrix (engl.: „CAS latency“, Volksmund „CL“) wird auf 3 bis maximal 6 Takte angehoben. Des weiteren werden keine halben Latenzen wie derzeit CL2.5 mehr unterstützt. Mehr dazu weiter unten.

- Terminierung der Leitungen direkt auf dem Chip. Eine Terminierung auf der Modulplatine ist nicht mehr nötig. Dies spart teure Platinenfläche, senkt die Materialkosten und verbessert die Signalqualität.

- DIM-Module mit 232 Pins anstatt derzeit 184.

- Der Aufbau und die sehr gute Kompatibilität von DDR-II ermöglicht Speichercontroller, die ohne Änderungen mit DDR-I Speicher oder DDR-II Speicher umgehen können.

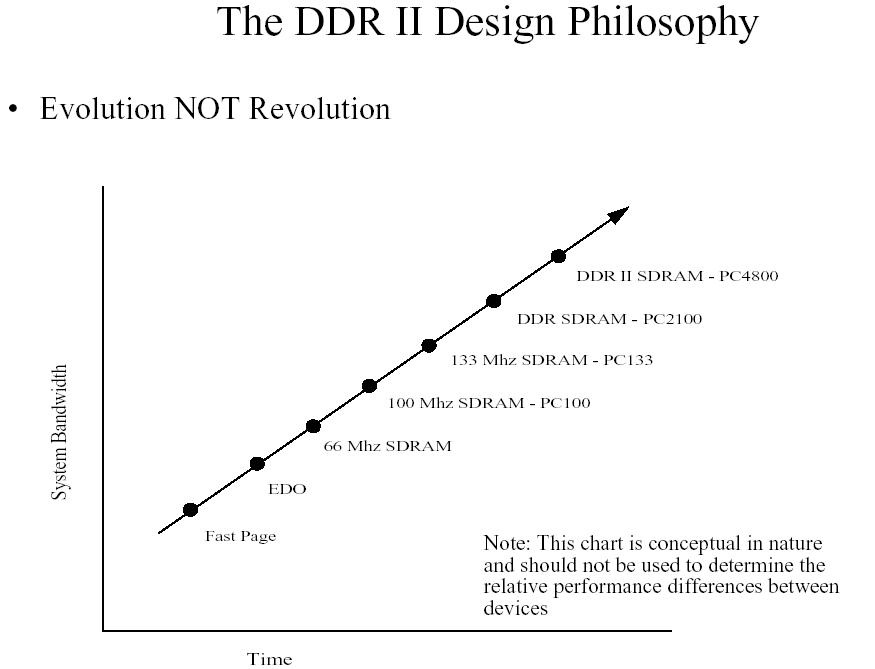

Der DDR-II Standard stellt damit eine direkte Weiterentwicklung des DDR-SDRAM Standards dar. Es wurden keine besonderen Veränderungen vorgenommen, sondern ausschliesslich auf größtmögliche Rückwärtskompatibilität und Kostensenkung hin entwickelt. Die erhöhten Latenzen von nun 3 bis 6 CAS Zyklen zeigen leider deutlich, dass die real erzielbare Geschwindigkeit eines einzelnen Speichermoduls kaum ansteigen wird. Die Rohfrequenzen, die an den Speicher angelegt werden, steigen zwar, dafür „wartet“ der Speicher aber mehr Takte ab, bis er Daten wirklich liefert. Im Endeffekt ist die Zeit, die bis zur Bereitstellung der gewünschten Daten vergeht, etwa gleichgeblieben. Die erhöhte Frequenz macht sich daher nur bemerkbar, wenn große, zusammenhängende Datenblöcke ausgelesen werden. Das kommt in der Realität jedoch nur selten vor.

Die Speicherindustrie tritt beim Design von DRAM auf der Stelle. Offenbar ist man nach dem Hickhack um Rambus nicht mehr gewillt, auf grundlegend neuen Techniken, die die designbedingten Nachteile von unoptimierten DRAM-Chips beseitigen könnten, zu setzen. DDR-II stellt eine möglichst geringfügige Änderung des SDRAM-Standards dar, damit die Hersteller ihre alten Maschinen weiterverwenden können und möglichst alle auf dem Markt benötigten DRAM-Speichertypen in einer Fabrik herstellbar sind.

Der Umschwung auf die Verpackung der Chips im BGA-Format war längst überfällig. Einige grosse Firmen mit sehr vielen alten Verpackungsmaschinen wie Samsung und Micron wollen jedoch auch 200MHz (DDR400) schnelle Speichermodule noch mit der alten Verpackungstechnik TSOP herstellen, um die Kosten so klein wie möglich zu halten.

Da die Geschwindigkeit der Prozessoren unaufhörlich weiter ansteigt, wird die Schere zwischen der Geschwindigkeit des Arbeitsspeichers und der Verarbeitungsgeschwindigkeit der Prozessoren auch in Zukunft weiter auseinandergehen. Dadurch sind die Designer von Chipsätzen gezwungen, alte Funktionen, wie Interleaving zwischen zwei Speichermodulen (heute als „dual-channel“ bezeichnet), wieder aus der Mottenkiste herauszukramen. Dies ist bei Desktopcomputern nicht sonderlich wirtschaftlich, aber notwendig, um die Prozessoren ausreichend schnell mit Daten versorgen zu können.

Abhilfe hätten grundlegend neue Techniken wie RDRAM gebracht. RDRAM zum Beispiel integriert Funktionen zur intelligenten Verwaltung des Speichers bereits in die Speicherchips. Außerdem vertragen die Chips weitaus höhere Arbeitsfrequenzen als DDR-SDRAM. Leider kam Rambus mit der Technik 1999 viel zu früh auf den Markt. Damals war sie noch weitaus teurer als SDRAM. Der Vorteil gegenüber der althergebrachten Technik war zudem in Benchmarks noch nicht ersichtlich. Der Ansatz war nichtsdestotrotz bahnbrechend. Hätte man RDRAM erst ein paar Jahre später zur Serienreife gebracht und mit der jetzt verfügbaren Prozesstechnik hergestellt, wäre es eine echte Alternative gewesen. So blieb die Entwicklung jedoch auf dem Niveau des 1999 zusammen mit Intel entwickelten „Direct Rambus“ stehen.

Leider kam der Ansatz zu früh und war nicht kostenlos, so dass die Hersteller auf die hohen Investitionskosten in neue Anlagen und die zu entrichtenden Lizenzgebühren an die Firma Rambus mit breiter Ablehnung reagierten. Dadurch ging bei Rambus der Wille verloren, die Technik weiterzuentwickeln. Weshalb etwas verbessern, das eh nicht genutzt wird? Stattdessen konzentrierte man sich darauf, Lizenzgelder aus anderen Quellen zu erhalten: Rambus überzog die Industrie mit völlig haltlosen Klagen und ruinierte damit den Ruf der im Ansatz sehr zukunftsträchtigen neuen DRAM-Speichertechnik „RDRAM“. Licht am Ende des Tunnels zeichnet sich nicht ab. Alle Roadmaps der Speicherhersteller zeigen auf weitere Beschleunigungsstufen von DDR-SDRAM, ohne die Architektur grundlegend zu überarbeiten.

Neueste Kommentare

3. Mai 2026

3. Mai 2026

29. April 2026

28. April 2026

23. April 2026

17. April 2026