Kommunikation ohne FSB

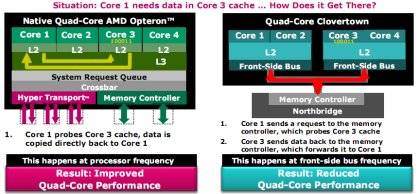

Anstatt zwei Doppelkerne über einen Front Side Bus kommunizieren zu lassen, werden bei den neuen Quad-Core Phenoms alle vier Kerne die Daten direkt auf dem CPU-Die austauschen. Durch dieses Vorgehen wird der Front Side Bus als potentieller Flaschenhals umgangen. Wenn ein Kern Daten aus dem Level-1 oder Level-2 Cache eines anderen Kerns beziehen will, werden diese Daten vom Controller über den L3-Cache an den anfordernden Kern geschickt. Der Controller kann auch auf den Hauptspeicher direkt zugreifen.

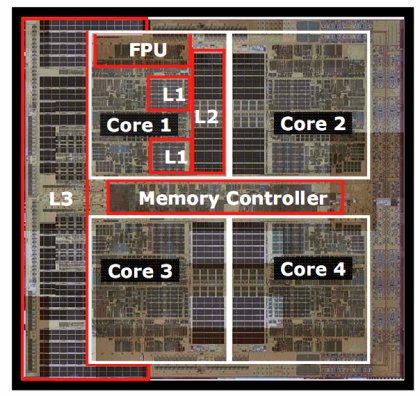

Jeder Kern ist mit 128 KByte L1-Cache ausgestattet, dieser teilt sich in jeweils 64 KByte für Instruktionen und Daten. Der L2-Cache jeden Kerns ist mit 512 KByte bemessen, der L3-Cache schließlich fasst 2 MByte. Diesen teilen sich die vier Kerne, der Zugriff erfolgt mit der vollen Taktrate. Diese Kommunikationsstruktur und Cache-Aufteilung auf dem Die bezeichnet AMD mit “Native Quad-Core” .

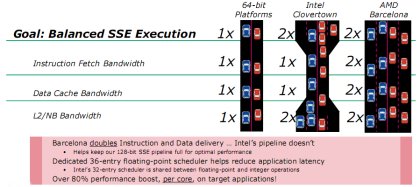

Ein weiterer Flaschenhals, den AMD addressieren will, liegt bei der SSE-Pipeline. 128bit SSE-Operationen können nun in einem Takt abgearbeitet werden. Bisher wurden dafür zwei Takte benötigt. Die verdoppelte Bandbreite der Pipeline dürfte auch Instruktionen zu einem Schub verhelfen, die mit 64bit breiten Registern arbeiten. In Verbindung mit dem dedizierten Scheduler für Fließkomma-Operationen mit 36 Einträgen sollen bei speziellen Anwendungen Performance-Steigerungen bis zu 80 Prozent möglich sein. Wie groß die Verbesserungen bei durchschnittlichen SSE-Anwendungen sein werden, bleibt abzuwarten.

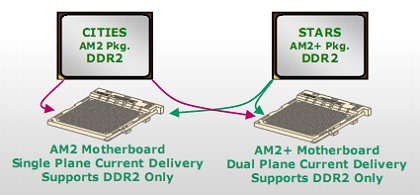

Mit Unterstützung von DDR3 SDRAM hält sich AMD noch zurück, man will hier erst noch abwarten. Dafür will man DDR2-1066 unterstützen. Momentan laufen allerdings noch Gespräche mit Standardisierungsgremium JEDEC. Auch wird DDR2-1066 ein dazu passendes Mainboard benötigen.

Neueste Kommentare

19. April 2024

17. April 2024

17. April 2024

5. April 2024

23. März 2024

22. März 2024